General Chairs

Sunita Chandrasekaran, University of Delaware,

USA

Guido Juckeland, Helmholtz Zentrum Dresden Rossendorf,

Germany

Program Chairs

Sridutt Bhalachandra, Lawrence Berkeley National

Laboratory, USA

Sandra Wienke, RWTH Aachen University,

Germany

Proceedings now available

The workshop proceedings are now available at https://link.springer.com/book/10.1007/978-3-030-74224-9.

COVID-19 Update: SC20 happening As a Virtual Event

SC20 will take place as a fully virtual event. As such our workshop has been rescheduled to Friday, November 13 from 10 a.m. to 2 p.m. EST. Speakers from accepted papers will prerecord their presentation and it will be streamed during the workshop with an interactive Q&A session afterwards. For more details on the planned virtual format please also consult the SC20 Virtual Event FAQ.

About the Workshop

Architectural trends indicate two directions. One being, heterogenous system equipped with accelerators for example the current system – Summit and the up and coming exascale systems such as Frontier and El Capitan and the other being homogeneous arm-based systems such as GW4 Isambard or the next Isambard 2 and Fugaku. A heavy reliance of future exascale machines for performance still seems to be ones with accelerators. One could even argue that the vector units of the curent HPC Arm processors are accelerators themselves. We are yet to see what will top the chart in a few years from now.

The ever-increasing heterogeneity in supercomputing applications has given rise to complex compute node architectures offering multiple, heterogeneous levels of massive parallelism. As a result, the ‘X’ in MPI+X demands more focus. Exploiting the maximum parallelism out of such systems necessitates sophisticated programming approaches that can provide scalable as well as portable solutions without compromising on performance. While an obvious expectation from the a programmer is to deliver portable solutions, thus avoiding duplicate programming effort, it is also important to understand the critical assessments of the possibilities and limitations of minimal-maintenance/performance portability approaches.

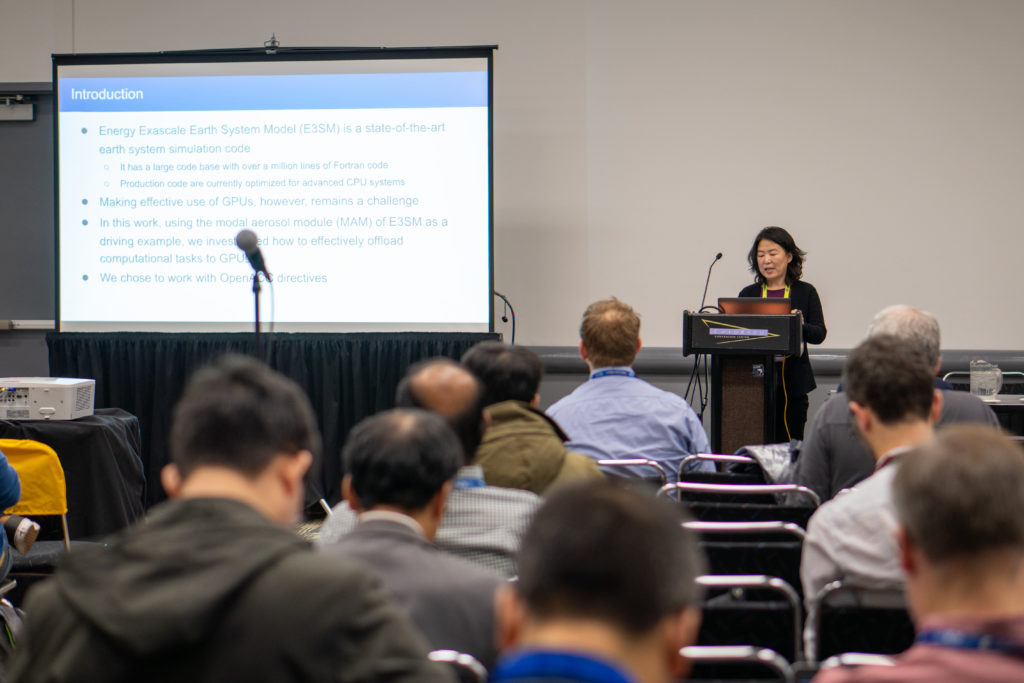

Literature shows that the abstraction can be raised at different levels i.e. at the high-level using directives such as OpenMP and OpenACC or at the language level using frameworks such as Kokkos and Raja or at a relatively lower level using OpenCL and/or SYCL/OneAPI. All of these efforts have certainly led to better compiler technologies.

Toward this end, the workshop will highlight transformational work along with improvements over state-of-art through the accepted papers and prompt discussion through keynote/panel that draws the community’s attention to key areas that will facilitate the transition to accelerator-based high-performance computing (HPC). The workshop aims to showcase all aspects of heterogeneous systems discussing innovative high-level language features, lessons learned while using directives to migrate scientific legacy code to parallel processors, compilation and runtime scheduling techniques among others.